# MAPPING THE COMMODORE

Ottis R. Cowper

A comprehensive memory guide for BASIC and machine language programmers.

# MAPPING THE COMMODORE 128

Ottis R. Cowper

Copyright 1986\(^\) COMPUTE! Publications, Inc. All rights reserved.

Reproduction or translation of any part of this work beyond that permitted by Sections 107 and 108 of the United States Copyright Act without the permission of the copyright owner is unlawful.

Printed in the United States of America

10 987654321

ISBN 0-87455-060-2

The author and publisher have made every effort in the preparation of this book to insure the accuracy of the programs and information However, the information and programs in this book are sold without warranty, either express or implied. Neither the author nor COMPUTE! Publications, Inc. will be liable for any damages caused or alleged to be caused direct!)', indirectly, incidentally, or consequentially by the programs or information in this book.

The opinions expressed in this book are solely those of the author and are not necessarily those of COMPUTE! Publications, Inc.

COMPUTE! Publications, Inc., Post Office Boy 5406, Greensboro, NC 27403, (919) 275-9809, is part of ABC Consumer Magazines, Inc., one of the ABC Publishing Companies, and is not associated with any manufacturer of personal computers. Commodore 64 and Commodore 128 are trademarks of Commodore Electronics Limited,

# **Contents**

| Preface                                             | v            |

|-----------------------------------------------------|--------------|

| Introduction                                        | vii          |

|                                                     |              |

| 1. Memory Organization                              | 1            |

| 2. Common Working Storage Area                      | 13           |

| 3. Bank 0 Working Storage Area                      | 115          |

| 4. RAM Usage                                        | 181          |

| 5. BASIC ROM                                        | 195          |

| 6. Machine Language Monitor ROM                     | 241          |

| 7. Screen Editor ROM                                | 267          |

| 8. I/O Chip Registers, Color RAM, and Character ROM | <b>1</b> 331 |

| 9. Kernal ROM                                       | 509          |

| Appendices                                          | 617          |

| <b>A.</b> Interrupts/Todrf <i>Heimarck</i>          | 619          |

| B. Bugs and Quirks in 128 ROM                       | 625          |

| C. Character, Screen, and Keyboard Codes            | 629          |

| D. Musical Note Frequencies                         | 645          |

| E. 64/128 Memory Map Cross Reference.               | 649          |

| P. BASIC Keyword Index                              | 657          |

| G. Index of Locations and Routines                  | 663          |

# **Preface**

The random access memory (RAM), read-only memory (ROM), and interface hardware chips in your Commodore 128 are like postal stations with hundreds of thousands of mailboxes, each of which can hold a single character, or byte of information. This book is a map of all of those memory locations, but it's more than just a list of addresses. It's also a thorough discussion of how the locations are used by the computer, and, more importantly, how you can take advantage of this information to write more powerful programs.

Why a mapping book? The 128's BASIC is the most powerful version yet in a Commodore computer. It could be argued that there's little need to get "under the hood" of the 128, since most of the functions that required lots of PEEKs and POKEs and an intimate understanding of internal hardware functioning in earlier models like the Commodore 64 can now be handled by simple BASIC statements on the 128. While it may be true that the 128's advanced BASIC makes programming easier, complete control over all the computer's features belongs only to those who understand the secrets of how the system operates. The purpose of this book is to unlock those secrets. The information is valuable for both beginning BASIC and advanced machine language programmers.

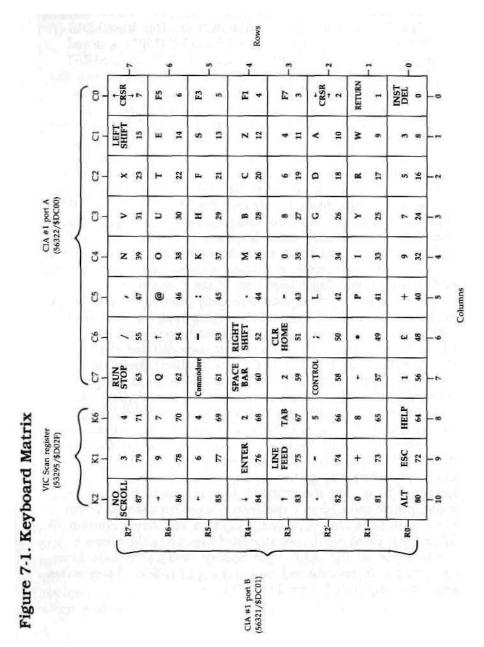

The standard features provided by the 128 are often plain vanilla, giving only the barest hint of the full capabilities of the computer. Would you like to set up a Dvorak keyboard that will work with almost any program? See the discussion of the keyboard table pointers in Chapter 2. How about an 80-column X 50-line screen display on your RGB monitor? The explanation of the VDC chip registers in Chapter 8 explains the necessary steps. Do you want to learn how the computer sends data over the serial bus? The process is described in Chapter 9. In fact, you'll find here the answers to most of your questions about the 128. And these answers are written in understandable, clear prose.

This book is the result of painstaking disassembly and deciphering of the Commodore 128 ROMs—a task that required gallons of midnight oil. Commodore's BASIC and operating

system are now nearly ten years old. The ROM routines have many twists and turns where various Commodore programmers have made additions and enhancements along the way. Although the 128 is internally quite different from the Commodore 64, there are similarities. As a result, several previous COMPUTE! books for the 64 provided invaluable assistance in attempts to understand some of the intricacies. I'm particularly indebted to Sheldon Leemon for *Mapping the Commodore 64*, and to Dan Heeb for his two volumes of *Commodore 64 and V1C-20 Tool Kit: BASIC* and *Kernal*.

Every effort has been made to insure that the information provided here is accurate, but in a project of this size and scope it is inevitable that some errors will creep in. Please send any corrections you may discover to the attention of the Book Editor at COMPUTE! Publications in Greensboro. You can also send electronic mail messages concerning this book to CompuServe user ID 73317,1143 or to BIX (Byte Information Exchange) user name ottis.

I'd like to salute my wife Gail for moral and logistical support far above and beyond the call of duty. I'd also like to thank the COMPUTE! staff for patience shown when this project dragged on months longer than anticipated. Finally, I'd like to dedicate this book to George and George, departing and arriving as the work took shape.

# Introduction

This memory map is a guide to the way a Commodore 128 in 128 mode uses and manipulates its RAM and ROM. No attempt is made here to provide detailed coverage of the 128's 64 mode. A Commodore 128 in 64 mode doesn't just emulate a Commodore 64; for all practical purposes it is a 64, with completely separate Kernal and BASIC ROM. The memory map of the Commodore 64 mode (and its BASIC 2.0) is covered in complete detail in COMPUTERS Mapping the Commodore 64. However, Appendix E discusses those 128 features available in 64 mode, and provides a cross reference of important memory locations for 64 and 128 modes—information that will be useful in translating Commodore 64 machine language routines for use in 128 mode.

Nor does this book make any attempt to map the way the 128's CP/M mode uses memory. CP/M is a large and complex operating system, and a CP/M mode memory map would easily fill another entire volume. Moreover, the major portion of CP/M is loaded from disk instead of being permanently stored in ROM. As a result, CP/M is subject to more frequent modification; so far, in the short life of the 128, there have been at least three major revisions. Detailed technical information on Commodore 128 CP/M is available in the book *CP/M Plus User's Guide /Programmer's Guide/System Guide*, available directly from Commodore.

Because this book is intended as a reference for intermediate to advanced BASIC and machine language programmers, no attempt is made to provide simple explanations of all the concepts discussed. The discussions assume familiarity with elementary computer concepts such as bits and bytes, and with memory quantity units such as a page (256 bytes) or a K (kilobyte, 1024 bytes). The book also assumes familiarity with the binary and hexadecimal numbering systems, although decimal equivalents are usually provided.

Hexadecimal numbers in the text are always preceded by a dollar sign (\$), the standard 8502 nomenclature for hex. Decimal numbers appear without any prefix. When you see a pair of numbers separated by a slash (/), the first number is

decimal and the second is hexadecimal, unless otherwise indicated. This book uses the machine language monitor's convention of preceding binary numbers with a percent (%) sign. For example, %11 indicates the binary value equivalent to decimal 3, not decimal 11.

When you see numbers mentioned in this book, it should be obvious from the context whether the number refers to an address or a value. Where there could have been confusion, the terms *value* and *location* or *address* specify what is meant. In keeping with common practice, only two hexadecimal digits are generally used when discussing addresses in the first page of memory (zero page). That is, addresses 0-255 are usually written as \$00-\$FF. Four hexadecimal digits are used for all other addresses. For example, location 256 will be written as \$0100,

By nature, the computer prefers to deal with whole numbers and doesn't handle fractions easily. Floating point is the method used to manipulate whole and fractional decimal numbers in 128 BASIC. Floating point also enables very large numbers to be handled in only a few bytes. All mathematical operations in BASIC are performed in floating point. (When you specify integer variables in a mathematical operation, the integer value is converted to floating point for the operation; then the result is reconverted to integer format.) However, because floating point is a rather complex subject, it is not explained in detail in this book even though it is mentioned extensively in Chapter 5. If you are interested in the inner workings of floating point, refer to the excellent discussion of the topic in COMPUTED VIC-20 and Commodore 64 Tool Kit: BASIC, by Dan Heeb. Although not written specifically for the 128, all the information about floating point applies to BASIC 7.0 as well.

Several terms used freely in this book need clarification. Most locations discussed in Chapters 2 and 3 are either *pointers*, *vectors*, or *flags*. Pointers and vectors refer to a pair of memory locations that hold an address. Two-byte address values in pointers and vectors are stored in low-byte/high-byte order. That is, the least significant byte of the address should be stored in the first byte of the pointer or vector, and the most significant byte of the address in the second pointer or vector byte.

The difference between pointers and vectors is that a pointer (as the name implies) points to an address from which

data is to be retrieved or in which data is to be stored, whereas a vector points to the address of a routine to be executed.

A flag is a memory location in which individual bits are used to signal particular conditions. A binary bit can have one of two conditions, %0 or %1 (also referred to as clear and set, respectively). The term comes from the analogy of flags, like those on rural mailboxes, that can be either lowered or raised (there's no half-mast in binary). An example is the active screen flag, location 215/\$D7. Bit 7 of the location is clear (%0) when the 40-column display is active, or set (%1) when the 80-column display is active. (You'll find that flag locations often use bit 7 because that bit can be tested very easily in machine language with the BMI and BPL instructions.)

Chapter 1 provides a brief introduction to the way the 128 arranges and manages its memory resources. That chapter and Chapter 4 are the only chapters in the book intended to be read from beginning to end. The remaining chapters describe the use or function of various areas of memory and should be used as an encyclopedic reference. The chapters generally cover memory in ascending address order, starting with zero page in Chapter 2 and ending with the Kernal jump table at the very top of memory in Chapter 9. Each entry in Chapters 2-9 consists of the decimal and hexadecimal address of the location or routine; a label, if one is commonly used; a short statement of the function of the location or routine; and a short description of how the location or routine is used.

# Memory Organization

The memory arrangement of a Commodore 128 in 128 mode is much different and more complex than that of any of its Commodore predecessors. As a result, it's necessary to understand how the 128 organizes and manages its memory resources before beginning a detailed examination of how those resources are used. Of the computer's three possible personalities, 128 mode is the default. Unless you take some other action—holding down the Commodore key, inserting a Commodore 64 cartridge, placing a CP/M boot disk in the drive—the computer comes up in 128 mode when you turn it on. As the native mode of the system, 128 mode makes the most complete use of the available memory resources.

You might be interested to learn that, while 128 mode is the default operating mode, the computer always starts out in CP/M mode. When you first turn on power, the Z80 microprocessor has control before the 8502 is allowed to take over. There are only a few signs of this: two short routines are copied into bank 0 RAM. One, at 65488/\$FFD0, is an 8502 ML routine that surrenders control to the Z80; the other, at 65504/\$FFEO, is a Z80 ML routine that surrenders control to the 8502. There are no routines in any of the 128 mode ROMs to perform this initialization. However, once the Z80 completes its initialization sequence, it turns the system over to the 8502 and 128 mode, and does not go back to CP/M mode unless a CP/M disk is booted.

### 128 Mode

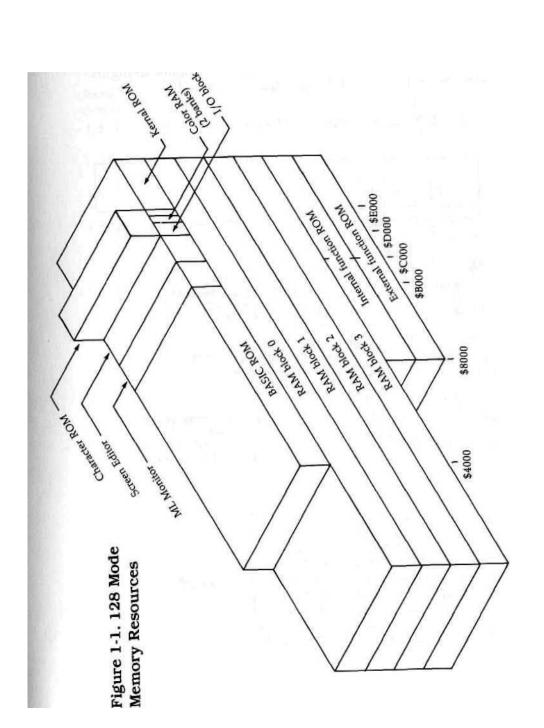

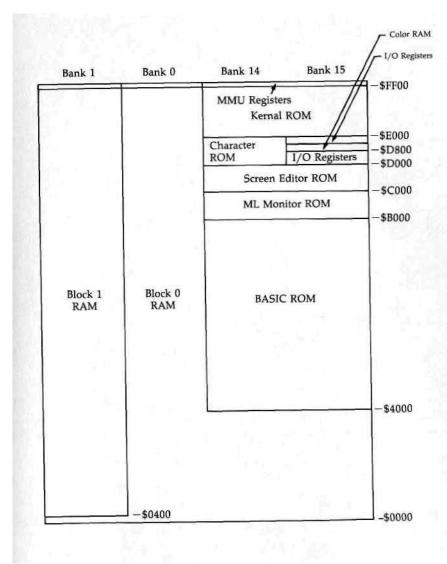

The 128 mode configuration includes 128K of random access memory (RAM) in two 64K blocks, a 28K BASIC interpreter in read only memory (ROM), a 4K machine language monitor in ROM, 4K of screen editor routines in ROM, 8K of Kernal operating system routines in ROM, a 4K character pattern ROM, and 4K of address space for hardware chip registers (with two separate IK banks of color RAM). The design also provides for

up to 32K of additional ROM internally and up to 32K of ROM on cartridge. The operating system can support two additional 64K banks of RAM, although the 128's design makes no provision for adding memory chips. In sum, that's 373K of address space, as illustrated in Figure 1-1.

This entire 373K address space must be manipulated by the 8502 microprocessor that is the brains of the 128, but an 8502 can directly access only 64K of memory at a time. So have in 128 mode over possible?

how is 128 mode even possible?

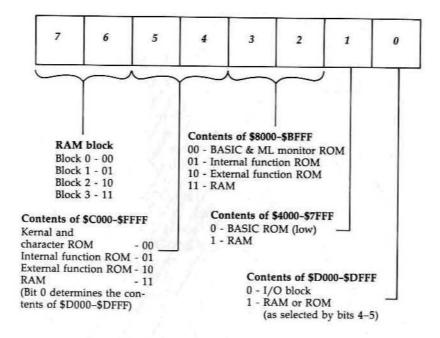

Memory Management Unit

The key is the MMU (Memory Management Unit), a special chip designed by Commodore's engineers to control the memory elements that are visible to the processor. The MMU is assisted by a companion device, the PLA (Programmable Logic Array). The PLA accepts a variety of system timing and control signals and combines them in various ways to create new control signals, taking the place of many separate discrete logic gates. Together, these chips assemble a 64K assortment of RAM, ROM, and I/O chips for the microprocessor to manipulate. The MMU is described in detail in Chapter 8, but the central feature of its memory control system is the configuration register. The value stored in this register, or in a related preconfiguration register, determines what elements the processor sees where. Only the 64K of memory elements defined by the MMU is available to the processor at any given time. Figure 1-2 illustrates the defined function of each bit in the register.

Since the configuration register is a standard eight-bit location, it can hold 256 different values (0-255/\$00-\$FF); thus, there are theoretically 256 possible configurations of memory resources in a Commodore 128. Fortunately, not all of the possibilities are equally useful, so you don't have to concern yourself with learning them all. The designers of the 128 operating system selected 16 of the most useful arrangements and defined them as banks.

Banks are a central feature of the 128, Banks are not fixed physical arrangements of RAM and ROM. Instead, the 128's banks are illusions created by the MMU to allow the microprocessor to manipulate much more memory than would otherwise be possible. There's nothing particularly sacred about the defined banks—you are free to create your own custom

configurations (see the discussion of the MMU in Chapter 8 for details)—but it is usually more convenient to work in one of the predefined banks. Table 1-1 shows the bank configurations defined by the 128's operating system.

Figure 1-2. MMU Configuration Register

**Table 1-1. Standard Bank Configurations**

Configuration Register Setting Addresses Contents Bank \$0000-\$FFFF RAM from block 0 0/\$00 63/\$3F RAM from block 0 \$0000-\$03FF i/\$oi 127/\$7F RAM from block 1 \$0400-\$FFFF RAM from block 0 \$0000-\$03FF 2/\$02 191/\$BF \$0400-\$FFFF RAM from block 2 \$0000-\$03FF RAM from block 0 3/\$03 255/SFF \$0400-\$FFFF RAM from block 3 RAM from block 0 4/\$04 \$0000-\$7FFF 22/\$16 \$8000-\$CFFF Internal function ROM I/O block **\$D000-\$DFFF** Internal function ROM \$E000-\$FFFF RAM from block 0 \$0000-\$03FF 86/\$56 5/\$05 \$0400-\$7FFF RAM from block 1 Internal function ROM \$8000-\$CFFF I/O block \$D000-\$DFFF Internal function ROM \$E000-\$FFFF RAM from block 0 \$0000-\$03FF 150/\$96 6/\$ 06 RAM from block 2 \$0400-\$7FFF \$8000-\$CFFF Internal function ROM I/O block \$D00O-\$DFFF \$EO00-\$FFFF Internal function ROM RAM from block 0 214/\$D6 \$0000-\$03FF 7/\$07 \$0400-\$7FFF RAM from block 3 Internal function ROM \$8000-\$CFFF I/O block \$D000-\$DFFF Internal function ROM \$E000-\$FFFF RAM from block 0 \$0000-\$7FFF 42/\$2A 8/\$08 \$8000-\$CFFF External function ROM I/O block **\$D000-\$DFFF** External function ROM \$E000-\$FFFF 106/\$6A \$0000~\$03FF RAM from block 0 9/\$09 RAM from block 1 \$0400-\$7FFF External function ROM \$8000-\$CFFF I/O block **\$D000-\$DFFF** External function ROM

\$EO00-\$FFFF

| Bank     | Configuration<br>Register<br>Setting | Addresses                      | Contents                                  |

|----------|--------------------------------------|--------------------------------|-------------------------------------------|

| 10/\$0A  | 170/\$AA                             | \$0000-\$03FF                  | RAM from block 0                          |

| 10/φ0/1  | 170/φ2111                            | \$0400-\$0511<br>\$0400-\$7FFF | RAM from block 2                          |

|          |                                      | \$8000-\$CFFF                  | External function ROM                     |

|          |                                      | \$D000-\$DFFF                  | I/O block                                 |

|          |                                      | \$EO00-\$FFFF                  | External function ROM                     |

| 11/\$OB  | 234/\$EA                             | \$0000-\$03FF                  | RAM from block 0                          |

|          |                                      | \$0400-\$7FFF                  | RAM from block 3                          |

|          |                                      | \$8000-\$CFFF                  | External function ROM                     |

|          |                                      | \$D00O-\$DFFF                  | I/O block                                 |

|          |                                      | \$E000-\$FFFF                  | External function ROM                     |

| 12/\$0C  | 6/\$06                               | \$0000-\$7FFF                  | RAM from block 0                          |

|          |                                      | \$8000-\$BFFF                  | Internal function ROM                     |

|          |                                      | \$C00O-\$CFFF                  | System ROM (screen                        |

|          |                                      |                                | editor)                                   |

|          |                                      | \$DO00~\$DFFF                  | I/O block                                 |

|          | 40/40                                | \$E00O-\$FFFF                  | System ROM (Kernal)                       |

| 13/\$0D  | 10/\$0A                              | \$0000-\$7FFF                  | RAM from block 0                          |

|          |                                      | \$8000-\$BFFF                  | External function ROM                     |

|          |                                      | \$CO00-\$CFFF                  | System ROM {screen                        |

|          |                                      |                                | editor}                                   |

|          |                                      | \$D000-\$DFFF                  | I/O block                                 |

| 1.4/0.00 | 1 /0 0 1                             | \$EO00-\$FFFF                  | System ROM (Kernal)                       |

| 14/\$0E  | 1/\$01                               | \$0000-\$3FFF                  | RAM from block 0                          |

|          |                                      | \$4000-\$CFFF                  | System ROM (BASIC                         |

|          |                                      |                                | 7.0, ML monitor, screen                   |

|          |                                      | \$D000-\$DFFF                  | editor)<br>Character ROM                  |

|          |                                      | \$E000-\$DITT                  | System ROM (Kernal)                       |

| 15/\$0F  | 0/\$00                               | \$0000-\$7FFF<br>\$0000-\$3FFF | RAM from block 0                          |

| 13/\$0F  | 0/\$00                               |                                |                                           |

|          |                                      | \$4000-\$CFFF                  | System ROM (BASIC 7.0, ML monitor, screen |

|          |                                      |                                | editor)                                   |

|          |                                      | \$D00O-\$DFFF                  | I/O block                                 |

|          |                                      | \$E00O-\$FFFF                  | System ROM (Kernal)                       |

|          |                                      |                                | , = (=======)                             |

Exceptions: In all banks, locations \$0000 and \$0001 are the 8502 processor's on-chip I/O port direction and data registers, and locations \$FFOO-\$FF04 are MMU configuration and load configuration registers.

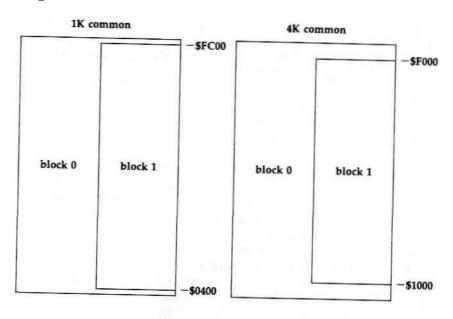

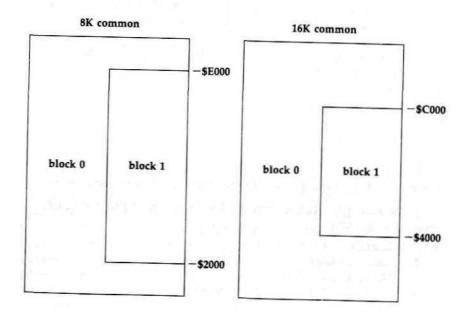

This banking system would be too unwieldy to be usable were it not for another capability of the MMU. Notice in the table that the contents of addresses 2-1023/\$0002-\$03FF are the same in all banks—RAM from block 0. (This particular feature is controlled by the MMU's RAM configuration register rather than by the configuration register.) The common area of RAM is another key to the operation of the 128. Since the area is visible to all banks, a collection of machine language subroutines is copied here from Kernal ROM when the system is initialized. These common subroutines, along with the fact that the MMU makes itself visible in every bank, allow routines in one bank to retrieve, store, and compare data in any other bank; to call subroutines in another bank; or to jump directly to routines in other banks. See the INDFET, INDSTA, INDCMP, JSRFAR, and JMPFAR entries in Chapter 2.

Actually, the operating system's banking scheme promises more than the 128 is able to deliver at this time. Of the four 64K blocks of RAM in the general operating system specification, only two (blocks 0 and 1) are present in the current version of the 128. The operating system was designed to leave open a gateway to future enhanced versions (perhaps a Commodore 256). The circuit board doesn't provide for the addition of RAM chips to populate blocks 2 and 3, nor does the current version of the MMU actually support them (bit 7 of the configuration register has no effect). Thus, banks 2, 3, 6, 7, 10, and 11 can be dismissed outright. If you try to access block 2 RAM (banks 2, 6, or 10), what you'll see is block 0 RAM, so banks 0 and 2, 4 and 6, and 8 and 10 are identical. An attempt to access block 3 will show block 1, so banks 1 and 3, 5 and 7, and 9 and 11 are also identical.

You should be aware that connecting one of the Commodore memory expansion modules (the 1700 for 128K or the 1750 for 512K) won't fill in these missing blocks of RAM. Memory in the expansion modules isn't connected directly to the computer's address lines. Instead, it must be accessed indirectly via the RAM Expansion Controller (REC) chip in the module. See Chapter 8 for more information about the REC and memory expansion modules. Memory in the expansion modules is also arranged in banks, but you shouldn't confuse these with the internal RAM blocks.

Banks 4, 5, and 12 are useful only if you have a function ROM chip installed in the free socket on the circuit board. Banks

8, 9, and 13 are useful only if you have a 128 ROM cartridge (called an external function ROM) plugged into the expansion port. If you attempt to access one of these ROM areas with no ROM chip installed, you'll get only random, unpredictable data. Since both internal and external function ROMs for the 128 are relatively rare, you can ignore those banks as well, unless you are writing a program specifically to put into ROM.

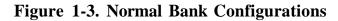

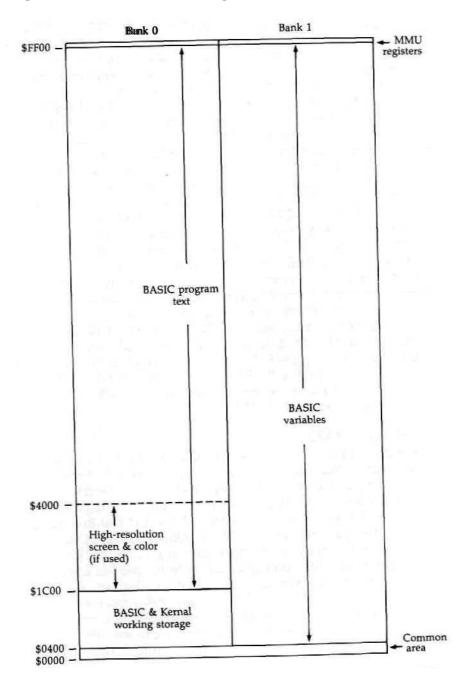

That leaves only four standard bank configurations which are generally useful: 0, 1, 14, and 15. Figure 1-3 shows the contents of these banks. All the memory areas mapped in this book appear in one or more of these banks. The lower IK of block 0 RAM is the heavily used common area of RAM which appears in every block. It's covered in Chapter 2. The next 7K of block 0 (1024-7167/\$0400-\$1BFF) is used as working storage by a variety of Kernal and BASIC routines. This area, visible in banks 0, 14, and 15, is covered in Chapter 3. Other RAM usage (banks 0 and 1) is discussed in Chapter 4. Chapter 5 covers BASIC ROM, visible in banks 14 and 15. Chapters 6 and 7 cover the machine language monitor and screen editor, respectively—both also visible in banks 14 and 15. Chapter 8 covers two of the possibilities for addresses 53248-57343/ \$D000-\$DFFF: the I/O block (including VIC-II chip color RAM) and character pattern ROM. Chapter 9 covers the Kernal ROM seen in banks 14 and 15.

There is one memory selection function not controlled by the MMU. The 128 has two separate IK banks of color RAM, both seen at the same addresses, 55296-56319/\$D800-\$DBFF in the I/O block. Bits 0 and 1 in the 8502 processor's on-chip data I/O port (location 1/\$01) determine which block will be seen by the processor and by the VIC chip. See the entry for location 1/\$01 in Chapter 2 for more information.

# Common Working Storage Area

The 128's memory management hardware has the ability to create common areas of memory—areas where the same memory will be seen regardless of the bank configuration. The system allows up to 16K at both the top and bottom of the processor's address space to be made common. However, the operating system uses only part of this capability, setting up a IK common area at the bottom of memory, locations 0-1023/\$0000-\$03FF. No matter what bank configuration you choose, the same block 0 RAM will be seen at these locations. It is this common area, and especially the common routines in page 2, that makes the 128's bank-switching operating system possible.

# **Zero Page: BASIC and Kernal Working Storage**

### 0-255/\$00-\$FF

The first 256 memory locations—collectively known as zero page—are special in any computer based on a 6502-family microprocessor like the 128's 8502. The processor has several special addressing modes which use this area. The zero-page addressing modes not only require less memory (two bytes per instruction instead of three); they also execute faster. As a result, system ROM routines make extensive use of these modes. Nearly every address in this page of memory is used by one or more system ROM routines. In fact, you'll notice in the entries for this page that a number of locations have multiple functions, and some have multiple entries.

One of the biggest challenges for machine language programmers is finding sufficient free space in zero page for their programs. Only four locations in the entire page (251-254/\$FB-\$FE) are completely unused by any system routine. Most of the locations in the range 10-143/\$OA-\$8F are used only by BASIC, not by the Kernal. Thus, many of those locations are free for machine language programs that do not require

BASIC. You should be aware that any value stored in zero page will be wiped out during a reset. The RAMTAS routine [\$E093], part of the reset sequence, clears locations 2-255/\$02-\$FF to zero. (You can prevent this by holding down the RUN/STOP key during the reset which will cause the RAMTAS step of the reset sequence to be skipped. In this case, the system will be left in the machine language monitor after the reset rather than in BASIC.)

Unlike other Commodore computers, the 128 has the ability to make the 8502 see zero page anywhere in memory. The MMU (memory management unit) chip has a feature which allows the processor to exchange zero page with another page so that references to zero page are directed to the alternate page, and references to addresses in the alternate page are directed to zero page. See the discussion of the MMU in Chapter 8 for details. The 128 does not normally make use of this feature; the default position for zero page is at the true zero-page locations.

The first two addresses in this page have a special function. The 8502 processor has a built-in I/O port, and it sees the registers for that port at locations 0-1/\$00-\$01. References to those addresses always affect the port; the processor will never see the first two bytes of RAM. These locations are not affected by the page-swapping feature. Regardless of where the remainder of zero page is currently seen, locations 0-1 are used exclusively to control the internal port.

### 0 \$00 D8502

Data direction register for processor's on-chip I/O port Bits 0-6 in this location control the direction of data flow for the seven I/O (input/output) lines on the 8502 microprocessor chip, labeled P0-P6. Setting a bit to %0 makes the corresponding line an input, and its state can be read at the corresponding bit position in location \$01. Setting a bit to %1 makes the corresponding line an output, and its state will be controlled by the setting of the corresponding bit position in location \$01. The value here is initialized to 47/\$2F by the IOINIT routine [\$E109], part of both the reset and RUN/STOP-RESTORE sequences. This sets lines 0-3 and 5 for output and lines 4 and 6 for input. Since only seven lines are provided, bit 7 is not used. That bit will retain whatever value is written to it, but its setting has no effect.

### 1 \$01 R85O2

Data register for processor's on-chip I/O port Each of the seven I/O lines on the 8502 microprocessor has a corresponding bit in this location (bit 7 is unused). The direction of data flow on the lines is controlled by location \$00. If an I/O port line is set for input, the corresponding bit here will reflect the state of the input line: %0 if the line is low (0 volts), or %1 if the line is high ( + 5 volts). While a line is set for input, values written to the corresponding bit have no effect. If an I/O port line is set for output, its state will be controlled by the corresponding bit in this location. Storing a %0 in the bit forces the output line to a low (0 volts) state, while storing a %1 in the bit sets the line to a high ( + 5v state).

The I/O lines are connected as follows:

Bits 0-1: The lines connected to these bits control which of the two IK blocks of color memory will be visible at 55296-56319/\$D800-\$DBFF when the I/O block is selected. For this purpose, the lines should always be configured as outputs. Unlike in the Commodore 64, these bits have no effect on whether RAM or ROM is selected at a given address. In the 128, memory management is the domain of the MMU chip. See Chapter 8 for more information.

Bit 0 controls which block the processor sees, while bit 1 controls which block the VIC chip sees. Setting either bit to %0 selects block 0, while a setting of %1 selects block 1. The setting of these bits is established during the screen-setup portion of the screen IRQ routine [\$C194], That routine sets both bits to %1 for text mode (GRAPHIC 0), or for the text portion of the split-screen modes (GRAPHIC 2 or GRAPHIC 4). For the bitmapped modes (GRAPHIC 1 or GRAPHIC 3) or for the bitmapped portion of the split-screen modes, bit 1 is set to %0. Thus, the VIC sees different blocks of memory for the modes, and drawing on the bitmapped screen will not disturb colors on the text screen. To manipulate these bits in other ways, the screen-setup portion of the IRQ routine must be disabled. Refer to the discussion of the color memory area in Chapter 8 for details on switching color blocks.

Bit 2: The line for this bit, known as the CHAREN line, determines whether the VIC chip will see character ROM in its current video bank. For proper functioning, the line should be configured as an output. While this bit is %0, the VIC chip

will see character ROM beginning at an offset of 4096/\$1000 from the start of the bank. The uppercase/graphics set will appear to occupy locations with offsets of 4096-6143/\$1000-\$17FF, and the lowercase/uppercase set will appear at offsets of 6144-8191/\$1800-\$1FFF. The character sets will be visible in all VIC video banks, not just banks 0 and 2 as was the case in the Commodore 64. Only the VIC chip will see the character ROM at these addresses; the processor will still see the locations as RAM or system ROM, depending on the address and bank configuration.

To disable this feature and allow the VIC chip to see RAM at the character set image addresses, the CHAREN bit must be set to % 1. However, this cannot normally be done directly because this bit has a shadow at location 217/\$D9. During the text mode-setup portion of the screen editor IRQ routine [\$C194], the value of bit 2 of the shadow location is copied into this bit. Thus, to change this bit you should set bit 2 of the shadow location instead. If the screen-setup portion of the IRQ routine is disabled (by storing the value 255/\$FF in location 216/\$D8, for example), the setting of this bit can then be changed directly. The IRQ routine always sets this bit to %1 for bitmapped screen modes or for the bitmapped portion of split-screen modes.

**Bit** 3: The line for this bit is connected to the CASS WRT (cassette write) line of the cassette port. The setting of this bit determines whether a signal is being written to the tape. For this purpose, the line must be configured as an output. See Chapter 9 for more information about the tape routines.

**Bit** 4: The line for this bit is connected to the CASS SENSE (cassette button sense) line of the cassette port. If the port line is configured as an input, this bit can be read to determine whether any buttons are currently pressed on the Datassette. When no buttons are pressed (or when no Datassette is connected to the port), this bit will be %1. Pressing any button will change this bit to %0. Unfortunately, the bit merely detects whether buttons are pressed, and cannot indicate which specific buttons. If you press FAST FORWARD when instructed to press PLAY, the 128 won't notice the difference.

**Bit** 5: The line for this bit controls the CASS MTR (cassette motor) line of the cassette port. When this bit is % 1, the power supply to the cassette motor, provided via the CASS

MTR line, is turned off. Setting this bit to %0 turns on the 9-volt power supply to the motor. The setting of this bit is controlled by a shadow location, the cassette motor interlock at 192/SCO.

**Bit** 6: The line for this bit is connected to the CAPS LOCK key on the keyboard. The line should be configured as an input to read the state of this key. The bit will return a %1 while the key is in the up position (CAPS LOCK off), and a %0 when the key is down (CAPS LOCK on). The status of this bit is read by the SCNKEY routine [\$C55D] during each system IRQ, and bit 4 of location 211/\$D3 will be assigned the opposite setting of this bit.

**Bit** 7: There is no I/O port line connected to this bit, so the value here is meaningless. The bit always returns a %0 when read.

### 2 \$02 BANK

Target bank for JMPFAR and JSRFAR

The value here determines the bank to which the JMPFAR routine [S02E3] will jump. Because the JSRFAR routine [\$02CD] calls JMPFAR as a subroutine, the value here also determines the destination bank for a JSRFAR. This location should be loaded with the number (0-15) of the desired bank before either JMPFAR or JSRFAR is used.

The BASIC SYS statement is implemented using JSRFAR. In that case, the value here is set from the value in location 981/\$03D5, which holds the parameter from the most recent BANK statement (15/\$0F by default). The BASIC routine that searches for a token in the runtime stack [\$4FAA] also uses location 2/\$02 for temporary storage.

When the monitor is entered at the break entry point [\$B003], this location is loaded with the bank number in which the system was operating when the BRK opcode was encountered. When the monitor is entered at the cold-start entry point [\$B000], as by the BASIC MONITOR command, this location is initialized to 15/\$0F (for bank 15). The monitor R command displays the value in this location as the first hexadecimal digit of the PC value. The register change (;) command can be used to alter the value stored here. The value determines the bank for the monitor G (go to routine) and J (jump to subroutine) commands, which use JMPFAR and JSRFAR, respectively.

3-4 \$03-\$04

### 3-4 \$03-\$04 PC

Target address for JMPFAR and JSRFAR

The values here determine the address to which the JMPFAR routine [\$02E3] will jump. Because the JSRFAR routine [\$02CD] calls JMPFAR as a subroutine, the value here also determines the destination address for a JSRFAR. These locations should be loaded with the desired address before either JMPFAR or JSRFAR is used. Contrary to the normal order of address bytes, the high byte of the target address should be stored in location 3/\$03 and the low byte in location 4/\$04.

When the monitor is entered at the break entry point [\$3003], these locations are loaded with the program counter contents stored on the stack when the BRK opcode was encountered. Because of the way the microprocessor handles BRK, this value will be two bytes beyond the address of the BRK (\$00) opcode. When the monitor is entered at the cold-start entry point [\$B000], as by the BASIC MONITOR command, these locations are initialized to 45056/\$B000 (the cold-start entry address). The monitor R command displays the value in these locations as the four rightmost hexadecimal digits of the PC value. The register change {;) command can be used to alter the value stored here. The value determines the target address for the monitor G (go to routine) and J (jump to subroutine) commands, which use JMPFAR and JSRFAR, respectively.

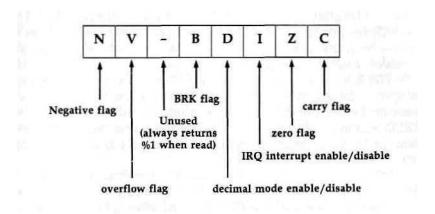

### 5 \$05 S-REG

Status register storage for JMPFAR and JSRFAR

The value in this location is transferred to the processor's status register when a routine is called with JMPFAR [\$02E3]. Because JSRFAR [\$02CD] also uses JMPFAR, the value here will also determine the initial status register value for a routine called with JSRFAR. You can use this location to set up particular entry conditions for the target routine. For example, certain system routines behave differently depending on whether the carry bit, bit 0 of the status register, is clear (%0) or set (%1) when the routine is called. You can specify the entry setting of the carry bit by setting bit 0 of this location. Figure 2-1 shows the function of the various status register bits. If you don't need any special entry conditions, it's best to set this location to 0/\$00.

5

The contents of the status register upon return from the target routine are stored in this location before return from JSRFAR, so you can read this location to determine the exit status of the routine. This is useful because system routines often use status register bits, particularly carry, to return information about the success of the operation performed by the routine.

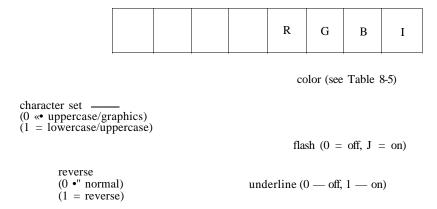

Figure 2-1. 8502 Processor Status Register

The BASIC 7.0 version of the SYS statement allows you to specify a status register value, which will be placed in this location before the JSRFAR to the specified address. The RREG statement can be used to read the value here. (The status register value returned by RREG is actually the contents of this location.)

When the monitor is entered at the break entry point [\$B003], this location is loaded with the status register contents stored on the stack when the BRK opcode was encountered. When the monitor is entered at the cold-start entry point [\$B000], as by the BASIC MONITOR command, this location is initialized to zero. The monitor R command displays the value in this location under the heading SR. The register change (;) command can be used to alter the value stored here. The value determines the status register contents for the monitor G (go to routine) and J (jump to subroutine) commands, which use JMPFAR and JSRFAR, respectively.

6 \$06

### 6 \$06 A\_REG

Accumulator storage for JMPFAR and JSRFAR

The value in this location is transferred to the processor's accumulator {A register) when a routine is called with JMPFAR

[\$02E3J. Because JSRFAR [\$02CD] also uses JMPFAR, the value here will also determine the initial accumulator value for a routine called with JSRFAR. You can use this location to set up a particular entry value for the target routine. The contents of the accumulator upon return from the target routine are stored in this location before return from JSRFAR, so you can read this location to determine the exit accumulator value. The JSRFAR routine itself uses the accumulator after return from the target routine, so you must look to this location for the accumulator value from the target routine.

The BASIC 7.0 version of the SYS statement allows you to specify an accumulator value, which will be placed in this location before the JSRFAR to the specified address. The RREG statement can be used to read the value here. (The accumulator value returned by RREG is actually the contents of this location.)

When the monitor is entered at the break entry point [\$B003], this location is loaded with the accumulator contents stored on the stack by the IRQ/BRK handler [\$FF17]. When the monitor is entered at the cold-start entry point [\$B000], as by the BASIC MONITOR command, this location is initialized to zero. The monitor R command displays the value in this location under the heading AC. The register change {}; command can be used to alter the value stored here. The value determines the accumulator contents for the monitor G (go to routine) and J (jump to subroutine) commands, which use JMPFAR and JSRFAR, respectively.

### $7 \$07 X_REG$

X register storage for JMPFAR and JSRFAR

The value in this location is transferred to the processor's X register when a routine is called with JMPFAR [S02E3J. Because JSRFAR [\$02CD] also uses JMPFAR, the value here will also determine the initial X register value for a routine called with JSRFAR, You can use this location to set up a particular entry value for the target routine. The contents of the X register upon return from the target routine are stored in this location before return from JSRFAR, so you can read this location

to determine the exit X register value. The JSRFAR routine itself uses the X register after return from the target routine, so you must look to this location for the X register value from the target routine.

The BASIC 7.0 version of the SYS statement allows you to specify an X register value, which will be placed in this location before the JSRFAR to the specified address. The RREG statement can be used to read the value here. (The X register value returned by RREG is actually the contents of this location.)

When the monitor is entered at the break entry point [\$B003], this location is loaded with the X register contents stored on the stack by the IRQ/BRK handler [\$FF17]. When the monitor is entered at the cold-start entry point [\$B000], as by the BASIC MONITOR command, this location is initialized to zero. The monitor R command displays the value in this location under the heading XR. The register change {;) command can be used to alter the value stored here. The value determines the X register contents for the monitor G (go to routine) and J (jump to subroutine) commands, which use JMPFAR and JSRFAR, respectively.

### 8 \$08 Y\_REG

to determine the exit Y register value.

Y register storage for JMPFAR and JSRFAR

The value in this location is transferred to the processor's Y register when a routine is called with JMPFAR [\$02E3]. Because JSRFAR [\$02CD] also uses JMPFAR, the value here will also determine the initial Y register value for a routine called with JSRFAR. You can use this location to set up a particular entry value for the target routine. The contents of the Y register upon return from the target routine are stored in this location before return from JSRFAR, so you can read this location

The BASIC 7.0 version of the SYS statement allows you to specify a Y register value, which will be placed in this location before the JSRFAR to the specified address. The RREG statement can be used to read the value here. (The Y register value returned by RREG is actually the contents of this location.)

When the monitor is entered at the break entry point [\$B003], this location is loaded with the Y register contents stored on the stack by the IRQ/BRK handler [\$FF17]. When

9 \$09

the monitor is entered at the cold-start entry point [\$B000], as by the BASIC MONITOR command, this location is initialized to zero. The monitor R command displays the value in this location under the heading YR. The register change (;) command can be used to alter the value stored here. The value determines the Y register contents for the monitor G (go to routine) and J (jump to subroutine) commands, which use JMPFAR and JSRFAR, respectively.

### 9 \$09 STKPTR

Stack pointer storage for JSRFAR and monitor This location is used in the JSRFAR routine [\$02CD] to record the value in the stack pointer upon return from the target routine. The value here doesn't affect the setting of the stack pointer; it merely records the exit value.

When the monitor is entered via either the cold-start entry point [\$B000] or the break entry point [\$B003], the current stack pointer value is stored in this location. The monitor R command displays the value in this location under the heading SP. The register change (;) command can be used to alter the value stored here. The value here is restored to the microprocessor's stack pointer before the JMPFAR in the G (go to routine) command routine. This location will hold the stack pointer value after a J (jump to subroutine) command, since that routine uses JSRFAR.

### 9 \$09 CHARAC or INTEGR

Working storage for various routines

This location is used for several different purposes by a variety

of BASIC routines. It serves as temporary storage in the routine which interprets ASCII characters as numeric values

[\$50A0]. It holds the value of the desired search character in

the routine which searches for a particular character in a

BASIC program line [\$52A2], and in the routine that puts a

string into the string pool [\$869A]. It holds the low byte of the

integer value generated in the BASIC INT routine [\$8CFB]. It

is also used for temporary storage of intermediate values while

performing BASIC AND or OR operations [\$4C86],

**\$0D** 13

### 10 \$0A ENDCHR

Working storage for various routines

This location is used for several different purposes by a variety of BASIC routines. It serves as a counter of the number of digits in the ASCII representation of a number during the routine which interprets the characters as a numeric value [\$50A0]. It holds the value of the character which terminates the search in the routine which looks for a particular character in a BASIC program line [\$52A2], and in the one that puts a string into the string pool [\$869A]. It is also used for temporary storage of intermediate values while performing BASIC AND or OR operations [\$4C86].

### 11 \$0B TRMPOS

Current screen column for TAB and SPC calculations The value in this location is used during the portion of the BASIC PRINT routine [\$5554] that handles the TAB and SPC functions. In the computation of the target column for the TAB or SPC, this location will hold the current cursor column value.

### 12 \$0C VERCK

BASIC LOAD/VERIFY flag

The same routine is used to perform both the load and verify operations, so this flag indicates which is being performed, A zero value here indicates a load operation, and a nonzero value indicates verify. The value here is set during the LOAD/VERIFY [\$9129] and DLOAD/DVERIFY [\$A1A4] routines. Both operations use the Kernal LOAD routine [\$F265], which has its own load/verify flag at location 147/\$93.

### 13 SOD COUNT

Working storage for various routines

This location is used for different purposes by several BASIC routines. It holds the most recently found token during program tokenization [\$430A]. In the routine that adds or deletes BASIC program lines [\$4DE2], this location holds the length of the current line. It is also used as a counter in the RREG routine [\$50BD], and as a counter in the subroutines that find or create array-variable elements.

14 \$0E

### 14 \$0E DIMFLG

Array dimension flag

This location is used during the routines that create array variables to indicate whether the routines are being called to as the result of a DIM statement. For a DIM statement, this location will contain a nonzero value; otherwise it will be set to 0/\$00. This flag is used in testing for the REDIM'D ARRAY ERROR condition.

### 15 \$OF VALTYP

Variable type flag

This location is used to indicate the type of variable currently being evaluated. A value of 0/\$00 indicates that the variable is numeric. A nonzero value indicates that the variable is string type. During the routine that finds or creates a variable [\$7AAF], this location is set to 0/\$00 if the variable is numeric type, or to 255/\$FF if it is string type.

### 16 \$10 INTFLG

Numeric variable type flag

If the variable currently being evaluated is numeric (see the entry for location 15/\$0F above), bit 7 of this location will be used to indicate the numeric type. If that bit is %0, the variable is standard (floating point) type. If the bit is %1, the variable is integer type. During the routine that finds or creates a variable [\$7AAF], this location will be set to 0/\$00 for floating-point variables or 128/\$80 for integer variables.

### 17 \$11 GARBFL

Working storage for various routines

This location is used for different purposes in several BASIC routines. During string evaluation, it is used as a garbage-collection flag. A zero value indicates that no garbage collection has been performed, while a nonzero value (1/S01) indicates that garbage collection has taken place. The location is also used as a quote mode flag during LIST; a value of 0/\$00 indicates that quote mode is off, while a nonzero value (1/\$01) indicates that quote mode is in effect. In addition, this location is used as temporary storage for the high byte of the disk status variable during the evaluation of the reserved variable DS.

**\$15** 21

### 18 \$12 **SUBFLG**

Integer/subscript prohibit flag

This location is used during the routine to find or create a variable [\$7AAF] to specify whether integer or subscripted (array) variables are allowed. While the value here is zero, the variable being evaluated can be of any type. The FOR and DEF routines store the value 128/\$80 here. For FOR, this prevents the use of integer or array variables as loop indexes. For DEF, this restricts the function definition to floating point variables and also prevents the parentheses in the function definition from being interpreted as indicating an array variable. This location is reset to zero after each variable is evaluated, and also during CLR [\$51F8].

### 19 \$13 INPFLG

Input source flag

BASIC uses a common input handling routine [\$56B2] for READ, GET (including GETKEY and GET#), and INPUT (including INPUT#). This location is used to indicate which operation is being performed. The value here will be 152/\$98 for a READ operation, 64/\$40 for a GET, or 0/\$00 for an INPUT.

### 20 \$14 TANSGN

Comparison type flag Tangent sign flag

The value in this location is used during the string and number comparison routine [\$4CB6] to specify the type of comparison being performed, A value here of 1 indicates greater than (>), 2 indicates equal (—), and 4 indicates less than (<). The values are cumulative, so a test for greater than or equal (>—) would result in a value here of 3 (1 + 2). This location is also used during the TAN function routine [\$9459] to indicate the sign of the resulting value.

### 21 \$15 CHANNL

Logical file number for BASIC input and output

The value in this location specifies the logical file from which BASIC will receive input and to which BASIC will direct output. The default value is 0/\$00, which indicates input from the keyboard and output to the screen. (Logical file 0 is reserved for the system's use; you cannot open logical file 0.)

22-23 \$16-\$17

Statements which get input or send output to other devices, such as GET#, INPUT#, and PRINT\*, will temporarily change the value here to the channel number specified in the statement.

The CMD statement can also be used to change the value here and direct all output to a specified logical file. However, you can't depend on CMD (or POKEing a value here) to keep all output flowing to the specified logical file. A number of other BASIC statements reset the value here to 0/\$00 each time they are executed, restoring default input and output devices. These statements include GET (and GET# and GETKEY), INPUT#, and PRINT\*.

### 22-23 \$16-\$17 LINNUM

Integer value of ASCII digit string

These are very busy locations, since the routine which reads ASCII characters from program text and converts the result to a two-byte line number value [\$50A0] stores its results here. Other routines which manipulate program lines, such as the one which adds or deletes program lines, will use these locations to hold the line number. Any statement which reads a line number, including GOTO, GOSUB, LIST, and so on, will expect to find the target line number in these locations. The TRAP destination line number is held here during the ERROR routine [\$4D3C], and the COLLISION target line number is held here during the GONE routine [\$4A9F].

Machine language programmers can store line number values in these locations, then jump into a BASIC routine at a point beyond the line number evaluation step. For example, a machine language program can enter a BASIC program at any line number by jumping into the GOTO routine with the target line number in these locations. The following section of code performs the equivalent of GOTO 100:

LDA #\$64 ;Place line number in \$16-\$17.

STA \$16

LDA #\$00

STA \$17

LDA #\$0F ;Bank number for BASIC ROM (15).

STA \$02

LDA #\$59

STA \$03

;Enter GOTO routine at \$59FB.

LDA #\$FB STA \$04

JMP \$02E3 ;Use JMPFAR to call routine.

\$24-\$25

### 24 \$18 TEMPPT

Pointer into temporary string descriptor stack

The value in this location points to the next available slot in the temporary string descriptor stack at 27-35/\$1B-\$23. This location can have the following values:

Value Meaning

27/\$IB no entries (stack empty)

3O/\$1E one entry 33/\$21 two entries

36/\$24 three entries (stack full)

### 25-26 \$19-\$1A LASTPT

Pointer to most recent descriptor stack entry

These locations hold the address of the most recent entry in the temporary string descriptor stack at 27-35/\$1B-\$23. Location 25/\$19 will hold the equivalent of the value in 24/\$18 less three, and location 26/\$1A will hold zero (it is assigned this value during the BASIC cold-start sequence). For example, when there are two entries on the stack, 24/\$18 will hold \$21, while these two locations will hold \$1E and \$00, corresponding to address \$001E, the address of the second entry in the stack.

### 27-35 \$1B-\$23 TEMPST

Temporary string descriptor stack

The three 3-byte entries here hold descriptors (length plus a 2-byte pointer to the starting address of the string in the string pool) for strings being evaluated or assembled. For strings being assigned to variables, the descriptor value generated here will be transferred to the variable table entry for that string,

### 36-37 \$24-\$25 INDEX

Multipurpose address pointer

These locations are used as an address pointer by several BASIC routines, including the one at 927/\$039F, which retrieves characters from bank 0 (BASIC program text), and the one at 951/\$03B7, which retrieves characters from bank 1 (BASIC string storage). Numerous BASIC routines call those character retrieval routines, including the one which inserts or deletes program lines [\$4DE2] and the one which updates variable tags while making space for a new variable. The

**38-39** \$26-\$27

pointer is also used in the LIST routine to read characters from the keyword table, and in the floating-point routines to copy floating values to and from the variable storage area in bank 1. In addition, location 36/\$24 is used for temporary storage during formula evaluation, and location 37/\$25 is used as a pointer into the ROM keyword tables when tokenizing program lines [\$43E2] or listing (detokenizing) program lines [\$5123].

### 38-39 \$26-\$27 INDEX2

Multipurpose address pointer

These locations are used as an address pointer by the routine at 960/\$03C0 which fetches characters from BASIC program text in bank 0. That routine is called by several other BASIC routines, including the one which adds or deletes program lines. These locations are also used by the ERROR routine [\$4D3C] as a pointer to the specified error message in the message table in ROM.

### 40-44 \$28-\$2C RESHO

Temporary storage area for multiplication and division This area is used to hold intermediate values during the BASIC routines that perform floating-point multiplication and division.

### 45-46 \$2D-\$2E TXTTAB

Start-of-BASIC-program pointer

The value in these locations points to the first address block 0 RAM used for BASIC program text. The value here is initialized to 7169/S1C01 during the BASIC cold-start sequence. In the Commodore 64, the value here was initialized to the value in the Kernal MEMSTR pointer, the bottom of memory established during the Kernal reset sequence. However, the 128 always initializes the same value here, without regard for the value in MEMSTR (2565-2566/\$0A05-\$0A06).

The only Kernal routines that change the value here are the ones that allocate or de-allocate a bitmapped graphics area for the GRAPHIC statement. When a bitmapped graphics area is allocated, BASIC program text is moved upward to start at 16385/\$4001, above the bitmapped graphics area at 7168-16383/\$1COO-\$3FFF. In this case, the values in these pointers will be adjusted accordingly. The value here will be reset to

**\$31-\$32 49-50**

7169/\$1CO1 when the graphics area is de-allocated and the BASIC program text is moved back down to its original position.

During the NEW and RUN routines, the CHRGET pointer (61-62/\$3D-\$3E) is initialized with a value one less than the address in these locations. You can store new values in these locations to change the starting position of BASIC program text—for example, if you wish to reserve free memory space in block 0 RAM below the program. However, two other steps are required to properly initialize the system to use the new starting position: You must also store the value 0/\$00 in the location immediately before the address specified here (BASIC requires that program text be preceded by a zero byte), and you must perform a NEW to reset other pointers to reflect the new start-of-BASIC position.

During execution of BASIC'S SAVE and DSAVE routines, the value here determines the starting address of the data to be saved.

### 47-48 \$2F-\$3O VARTAB

Start-of-variables pointer

The value in these locations points to the first address in block 1 RAM used for scalar (nonarray) variable storage. The value here is initialized to 1024/\$0400 during the BASIC cold-start sequence, and no other system routine changes that setting. You can store new values in these locations to change the starting position of the variable table—for example, if you wish to reserve free memory space for data storage in block 1 RAM below the variables. However, to properly initialize the system to use the the new starting position, you must perform a CLR to reset other pointers to reflect the new start-of-variables position. During the CLR routine [\$51F8] {which is also performed during NEW and BASIC cold start), the start-of-arrays pointer (49-50/\$31-\$32) and the end-of-arrays pointer (51-51/\$33-\$34) are also set to the value in these locations.

### 49-50 \$31-\$32 ARYTAB

Start-of-arrays pointer

The value in these locations points to the first address in block 1 RAM used for the storage of array variables, which is also one location above the last address used for array variables. The value here is initialized to the start-of-variables value in

**51-52** \$33-\$34

locations 47-48/\$2F-\$30 during the CLR routine [\$51F8] (which is also performed during NEW and BASIC cold start).

#### 51 -52 \$33-\$34 STREND

Start-of-free-memory pointer

The value in these locations points to the lowest address in block 1 RAM available for the storage of strings, which is also one location above the last address used for array variables. The value here is initialized to the start-of-variables value in locations 47-48/\$2F-\$30 during the CLR routine [\$51F8] (which is also performed during NEW and BASIC cold start). When the value here equals the value in location 49-50/ \$31-\$32, no arrays are being used. The function FRE(1) will return the difference between the value here and the one in locations 53-54/\$35-\$36, representing the remaining amount of memory available for string storage. When the value in 53-54/\$35-\$36 (the FRETOP pointer) reaches the value here, garbage collection is performed. If garbage collection cannot remove enough unused strings to create free space between the address here and the one pointed to by FRETOP, an OUT OF MEMORY error occurs.

#### 53-54 \$35-\$36 FRETOP

Bottom-of-string-space pointer

The value in these locations points to the lowest address in block 1 RAM used for the string pool. All character strings used in a BASIC program are stored in the area of block 1 between the address pointed to in 57-58/\$39-\$3A and the address pointed to here—an area called the string pool. Each active string here will have a descriptor in the variable array table areas at the bottom of block 1, or in the temporary descriptor stack at 27-35/\$1B-\$23. The pool may also contain inactive strings that the program is no longer using. The value here is initialized to the top-of-memory value in locations 57-58/\$39-\$3A during the CLR routine [\$51F8] (which is also performed as part of NEW and the BASIC cold-start sequence).

When the value here equals the value in location 57-58/\$39-\$3A, no strings have yet been used. Strings are added from the top of memory downward. When the value here reaches the value in 51-52/\$33-\$34, garbage collection is

\$3B-\$3C 59-60

performed to remove inactive strings. If garbage collection cannot remove enough unused strings to create free space between the address here and the one in 51-52/\$33-\$34, an OUT OF MEMORY error occurs. The function FRE(l) will return the difference between the value here and the one in locations 51-52/\$33-\$34, the amount of free memory remaining for string storage.

#### 55-56 \$37-\$38 FRESPC

Temporary pointer into the string pool

These locations are used by the routines that add strings to the string pool as a pointer to the currently referenced string, and as a pointer to the current string during the garbage collection routines.

## **57-58 \$39-\$3A** MAX\_MEM\_1

Top-of-memory pointer

The value in these locations determines the highest address in block 1 RAM available for the string pool. (Actually, the address value here will be one location beyond the highest location used for the string pool.) The string pool is filled downward from the address specified here. The value in locations 53-54/\$35-\$36 specifies the address of the bottom of the pool. When the value in those locations equals the value here, the pool is empty. The BASIC cold-start routine initializes these locations to 65280/\$FFO0, one location beyond the highest contiguous address in block 1 RAM (MMU registers are seen at 65280-65284/\$FF0O-\$FFO4 in all memory configurations). You can reduce the value here to reserve memory at the top of block 1 for other purposes such as data storage. However, when you change the value here you should also execute a CLR statement [\$51F8] to reset the other string pool pointers,

# 59-60 \$3B-S3C CURLIN

Current BASIC line number

These locations hold the line number of the BASIC program line currently being executed. After each program line is executed, the routine which executes BASIC program lines [\$4AF3] will load these locations with the number of the next line to be executed. The value here is used by various other

61-62 \$3D-\$3E

BASIC routines that need to know which line is currently being executed, The value here is stored in locations 4608-4609/\$1200-\$1201 by the routine that processes STOP or END [\$4BCA]. The value stored in those locations will be transferred back here by the CONT routine [\$5A60]. The value here will be stored in locations 4617-4618/\$1209-\$120A when an error is processed by the ERROR routine [\$4D3C]. The value in those locations will be transferred back here by the RESUME routine [\$5F62],

#### 61-62 \$3D-\$3E TXTPTR

Pointer for main BASIC character retrieval routine These locations serve as the pointer into BASIC text for the CHRGET routine, BASIC'S primary character retrieval routine. In earlier Commodore computers, the entire CHRGET routine was in zero page. The 128's CHRGET is located higher in the common area, beginning at address 896/\$0380, and only the pointer is kept in zero page. CHRGET is designed to retrieve the next nonspace character of BASIC text, so the first step in CHRGET is to increment the address here. The routine also has an alternate entry point called CHRGOT at 902/\$0386, which retrieves the current character (the one at the address here) without incrementing the pointer.

The NEW, RUN, and LOAD routines all call the subroutine [\$5254] which initializes this pointer to one byte before the start-of-BASIC value in locations 45-46/\$2D-\$2E. Because the CHRGET routine is so heavily used, many BASIC routines affect the value here. For example, any of the routines which send the program to another line, such as GOTO, GOSUB, THEN, and so on, must replace the current value here with the address of the target line. The value here is stored in locations 4610-4611/\$1202-\$1203 by the routine that processes STOP or END [\$4BCA]. The value stored in those locations will be transferred back here by the CONT routine [\$5A60]. The value here will be stored in locations 4622-4623/\$120E-\$120F when an error is processed by the ERROR routine [\$4D3C], The value in those locations may be transferred back here by the RESUME routine [\$5F62].

The value here is also used as a pointer for the alternate character retrieval routine at 969/\$03C9, which fetches the current text character without CHRGET's test for character type.

**\$43-\$44 67-68**

#### 63-64 \$3F-\$40 FNDPNT

Working pointer for various routines

These locations are used as a working pointer into the runtime stack at 2048-2559/\$0800-\$09FF by the routines that search for tokens in the stack. The RENUMBER routine [\$5AF8] uses these locations as an end-of-program pointer. The PRINT USING routine [\$9520] uses the routine at 939/\$03AB (which uses these locations as a pointer) to retrieve characters from the template pattern string in block 1 RAM.

#### 65-66 \$41-\$42 DATLIN

Line number of current DATA statement

These locations hold the line number of the BASIC program line containing the DATA statement from which DATA items are currently being read. These locations are updated by the subroutine that searches for the start of the next DATA statement: [\$57CA], called during execution of the READ statement. The value here isn't used by any system routine, but it can be very helpful when you're debugging a program containing DATA statements. Whenever a program stops with an ILLEGAL QUANTITY or TYPE MISMATCH error message in a line containing a READ statement, it's very likely that the error is actually in the DATA line rather than the line specified in the error statement (the one which contains READ). You can find the line number from which the last, possibly erroneous, DATA item was read using PRINT PEEK(65) + 256 \* PEEK(66).

## 67-68 \$43-\$44 DATPIR

Pointer to next DATA item

These locations are used as a pointer to the address at which the search for the next available DATA item will begin. The subroutine that searches for the next DATA item [\$57CA], called during execution of the READ statement, will update the value here to point to the start of the next DATA item. The RESTORE statement, when used without a line number parameter, resets the value here to the starting address of BASIC program text (from locations 45-46/\$2D-\$2E), That RESTORE subroutine is also called as part of the CLR routine, which in turn is called as part of RUN. Thus, the search for DATA items normally begins at the first program line. The

69-70 \$45-\$46

RESTORE statement can be used with a line number parameter to change the value here. In that case, the pointer value will be reset to the starring address of the specified line. The specified line need not contain a DATA statement. It merely specifies the line from which the search for the next DATA statement will begin.

# 69-70 \$45-\$46 **INPPTR**

Text pointer for input

The common input routine [\$56B2], used in the execution of the GET, GETKEY, GET#, INPUT, INPUT\*, and READ statements, uses these locations as a pointer to the characters to be read as input. The value here will be transferred into the CHRGET pointer at 61-62/\$3D-\$3E so that CHRGET can be used to retrieve characters from the input. The GET, GETKEY, and GET\* statements will initialize the value here to 513/\$0201, an input buffer location set to 0/\$00 to cause the input routine to read the next character. The INPUT and INPUT\* statements will initialize the value here to 511/\$01FF, a location immediately before the input buffer set to 44/\$2C, the code for the comma character. The actual input will be in the input buffer beginning at 512/\$0200. The READ statement will initialize these locations with the starting address of the next DATA item (from locations 67-68/\$43-\$44).

#### 71-72 \$47-\$48 VARNAM

Current variable name

These locations are used during the routine to find or create a variable [\$7AAF] to hold the compressed (two-byte) form of the specified variable name. This compressed form will then be used as a search pattern to check whether a variable of the same name and type currently exists. If not, the characters here will be used as the name for the new variable.

## 73-74 \$49-\$4A VARPNT

## Pointer to variable descriptor

These locations are used as a pointer to the first byte of the descriptor for the variable—the address of the location just beyond the two-character name in the variable table entry for the variable. The value here is set upon exit from the routines to find [\$7AAF] or create [\$7B90] a variable. The FN (user-

\$4F 79

defined function) routine will load these locations with the address of the descriptor for the dummy variable in the function definition.

## 75-76 \$4B-\$4C FORPNT

Variable descriptor pointer and working storage

These locations are used during the routine that assigns variable values (LET [\$53C6]) as a pointer to the variable value or string descriptor. For numeric variables, the address here will be the location in block 1 RAM where the value will be stored. For string variables, the address here will be the location in block 1 RAM where the length and pointer into the string pool for the string will be stored. The FOR statement uses the value here to find the address of the value for the loop index variable.

For the WAIT statement [\$6C2D], location 75/\$4B holds the test byte pattern and location 76/\$4C holds the mask byte pattern. Location 75/\$4B is also used as an index into the current line during the routine to list BASIC program lines [\$5123],

#### 77-78 \$4D-\$4E VARTXT

Temporary storage for text pointer

These locations are used for temporary storage for the CHRGET pointer value from 61-62/\$3D-\$3E during the common input routine [\$56B2], which uses CHRGET to retrieve characters from the input source location. Location 77/\$4D is also used during the numeric expression evaluation routine [\$77EF] as a flag to indicate when the end of the expression has been reached.

#### 79 \$4F OPMASK

Relational operator flag

When the main expression evaluation routine [\$77EF] finds a relational operator ( $\langle , = , \text{ or } \rangle$ ) in the current expression, it stores a value here indicating which operator has been found. For greater than ( $\rangle$ ) operations, the value here will be 1. For equals (=), the value will be 2; for less than ( $\langle$ ) it will be 4. When the expression is evaluated, this value will be transferred to location 20/\$14.

80-81 \$50-\$51

80-81 \$50-\$S1 DEFPNT

Defined function pointer and working pointer

These locations are used by the routine that retrieves bytes

from the variable table entry for a function definition (FN).

That routine [\$42CE] uses these locations as a pointer for one

of the bank 1 character retrieval subroutines [\$03AB]. These

locations are also used as a working pointer by one of the

routines that reads values during garbage collection. That routine [\$42FB] also uses a bank 1 data retrieval subroutine [\$03AB].

The routine that allocates the bitmapped graphics area [\$9F4F]

uses these locations to hold the number of bytes that must be

moved upward to make room for the graphics area.

## 80-84 \$50-\$54 TEMPF3

Temporary storage for floating-point value These locations are used to temporarily hold the floating-point value of the exponent during the routine to handle the exponentiation (T) operator [\$8FC1].

#### 82-83 \$52-\$53 DSCPNT

Variable address storage and working pointer The routine that creates space in the string pool for a new string variable uses these locations to temporarily store the address of the variable table entry. These locations are also used as a pointer by the routine that retrieves characters from the string pool for the LEFT\$, RIGHT\$/ and MID\$ functions [\$42D8].

# **\$5 \$55 HELPER**

HELP flag

Bit 7 of this location is tested in the routine which lists BASIC program lines [\$5123] to determine whether the line is being displayed by LIST or by HELP. When the bit is % 1, the subroutine at 22956/\$59AC will be called to highlight the portion of the line where the most recent error occurred. The HELP statement routine [\$5986] sets bit 7 to %1 before it calls the line-listing routine, and clears it to %0 afterwards.

# 86-88 \$56-858 JMPER

BASIC function execution vector

This vector is used to execute the routines that handle BASIC functions. Location *S6/\$56* is initialized during the BASIC

\$5D-^\$5F 93-95

cold-start sequence with the value 76/\$4C, the 8502 JMP opcode. The function dispatch routine [\$4BF7] loads 87-88/\$57-\$58 with the address of the routine that performs the desired function operation. A JSR \$0056 instruction then executes the function-handling routine.

# 89-93 \$59-\$5D TEMPF1

Floating-point work area

These locations are used as a temporary floating-point work area during the series evaluation routine [\$9086] for the LOG, SIN, COS, TAN, and ATN functions. Location 89/\$59 is also used for temporary storage during the routine [\$9D7C] which subtracts the contents of one pair of bitmapped graphics storage locations from the contents of another pair of locations.

#### 90-91 \$5A-\$5B ARRYPNT

Multipurpose working pointer